文章目录

时序逻辑__滞后一个像素

最近又重新拿起了VGA,因为需要要把像素点绝对的精确,因此……

在显示汉字的时候,很郁闷很郁闷的问题,怎么老是在最左边显示了汉字最右边的一列呢???怎么都想不通,郁闷……

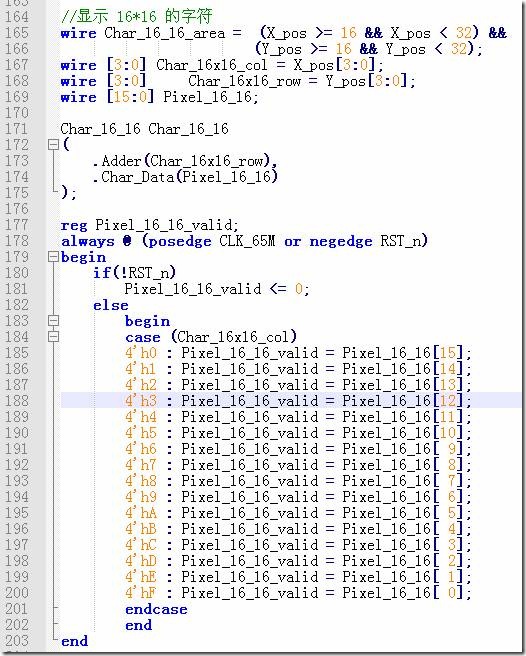

程序如下:

很郁闷,明明是对的,可是为什么是错的呢??

崩溃,怎么改都不对。

崩溃了一个小时候突然想到,把显示的内容向右平移一个像素点,不久OK 了吗??,于是在X坐标判断语句中加了1,好了。

可是,这只是结果,结果是好了,却不知道过程到底是如何。我只知道滞后了一个时钟周期即一个像素点,但是不知道该如何面对。

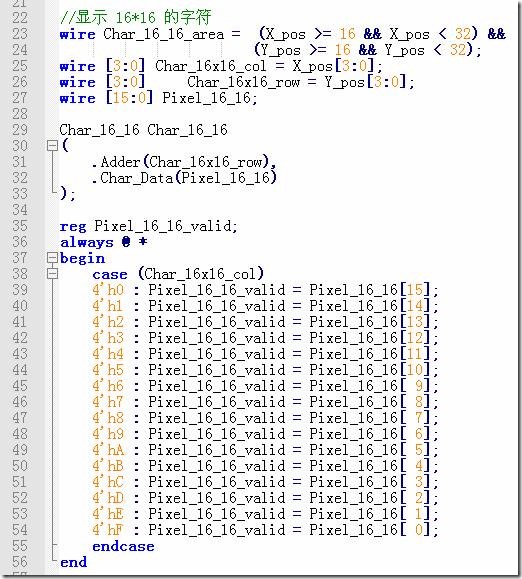

继续崩溃了一会儿……突然想到,既然那个输出汉字像素点滞后了一个时钟,那何不用组合逻辑呢??一切错误从此解决了。

不由自主,想起了当年用VHDL 写的时候,也是汉字向右便宜了,那时候能力尚欠,不知道,现在终于解决了,哈哈,释怀啊……

以前有个人告诉我,他都不用组合逻辑的,他只用时序逻辑,说时序逻辑稳定,怎么怎么的,我似懂非懂的 哦哦哦……

现在知道了,其实很多时候,时序逻辑就会让你滞后一个时钟周期,在主要时序非常准确的时候,这就需要考虑到了,不能忽略;当然你要是再点亮发光二极管,这当然是无需过问的。。很明显,时序的精确……

因此,等设备到达了一定的速度,需要非常准确稳定的时序的时候,组合逻辑、时序逻辑也要慎用啊,

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关

此时此刻,VGA上汉字显示相当标准,哈哈 ,组合逻辑真好……