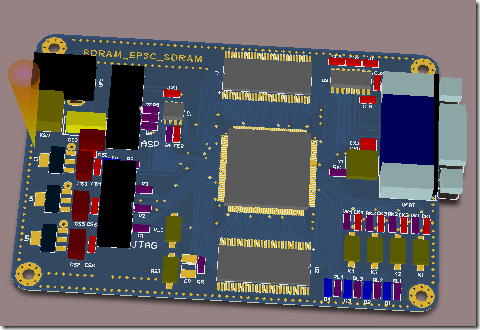

一个优秀的Layout,一块好的板子,并不是随便布线连同就可以实现电路要求的,凡事都得谨慎,此处别处摘要,讲述SDRAM类高速器件布线规则:

如果你没有信号完整性的知识和对传输线的认识,恐怕你很难看懂,如果你看不懂,那么请按这样一个通用的基本法则做:

(1)DDR和主控芯片尽量靠近

(2)高速约束中设置所有信号、时钟线等长(最多允许50mils的冗余),所有信号、时钟线长度不超过1000mils

(3)尽量0过孔,元件层下面一定要有一个接地良好的地层,所有走线不能跨过地的分割槽,即从元件层透视地层看不到与信号线交叉的地层分割线。

这样的话200M的DDR基本上是没有太大问题。其它的一些3W 20H法则就能做到尽量做到吧

时钟信号:以地平面为参考,给整个时钟回路的走线提供一个完整的地平面,给回路电流提供一个低阻抗的路径。由于是差分时钟信号,在走线前应预先设计好线宽线距,计算好差分阻抗,再按照这种约束来进行布线。所有的DDR差分时钟信号都必须在关键平面上走线,尽量避免层到层的转换。线宽和差分间距需要参考DDR控制器的实施细则,信号线的单线阻抗应控制在50~60 Ω,差分阻抗控制在100~120 Ω。时钟信号到其他信号应保持在20 mil*以上的距离来防止对其他信号的干扰。蛇形走线的间距不应小于20 mil。串联终端电阻RS值在15~33Ω,可选的并联终端电阻RT值在25~68 Ω,具体设定的阻值还是应该依据信号完整性仿真的结果。

数据信号组:以地平面为参考,给信号回路提供完整的地平面。特征阻抗控制在50~60 Ω。线宽要求参考实施细则。与其他非DDR信号间距至少隔离20 mil。长度匹配按字节通道为单位进行设置,每字节通道内数据信号DQ、数据选通DQS和数据屏蔽信号DM长度差应控制在±25 mil内(非常重要),不同字节通道的信号长度差应控制在1 000 mil内。与相匹配的DM和DQS串联匹配电阻RS值为0~33 Ω,并联匹配终端电阻RT值为25~68Ω。如果使用电阻排的方式匹配,则数据电阻排内不应有其他DDR信号。

地址和命令信号组:保持完整的地和电源平面。特征阻抗控制在50~60 Ω。信号线宽参考具体设计实施细则。信号组与其他非DDR信号间距至少保持在20 mil以上。组内信号应该与DDR时钟线长度匹配,差距至少控制在25 mil内。串联匹配电阻RS值为O~33 Ω,并联匹配电阻RT值应该在25~68 Ω。本组内的信号不要和数据信号组在同一个电阻排内。

]

控制信号组:控制信号组的信号最少,只有时钟使能和片选两种信号。仍需要有一个完整的地平面和电源平面作参考。串联匹配电阻RS值为O~33 Ω,并联匹配终端电阻RT值为25~68 Ω。为了防止串扰,本组内信号同样也不能和数据信号在同一个电阻排内。