声明:本文为原创作品,版权归akuei2及黑金动力社区(http://www.heijin.org)共同所有,如需转载,请注明出处http://www.cnblogs.com/kingst/

5.6 实验十九:VGA封装

在笔者还没有开始写这本笔记之前,笔者和大众的新手一样,都喜欢在网络上找资料。

有一篇论文“基于FPGA的VGA接口”中的实验,笔者很感兴趣,但是论文始终是论文,论文的东西都是用来毕业,瞎了笔者的狗眼。笔者就在那个时候开始突发奇想:“有没有什么的办法,以最小的条件,来实验该论文中的内容呢?”

在此刻,阅读这章笔记的时候,读者是否对“封装”或者“接口”有一个概念了吧?

同样的事实,VGA模块也需要封装成为VGA接口。

|

图像分辨率 |

16 x 16 |

|

图像颜色 |

点阵 |

|

图像显示位置 |

X = 3 ,Y = 2 |

|

显示标准 |

800 x 600 x 60Hz |

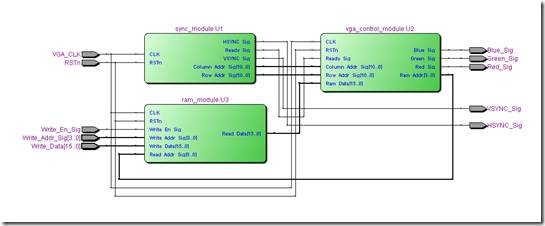

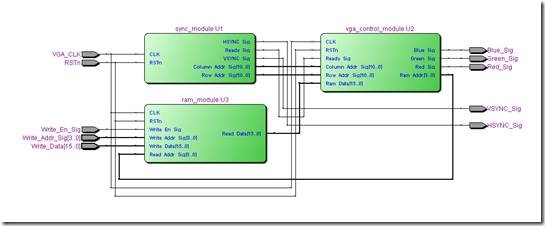

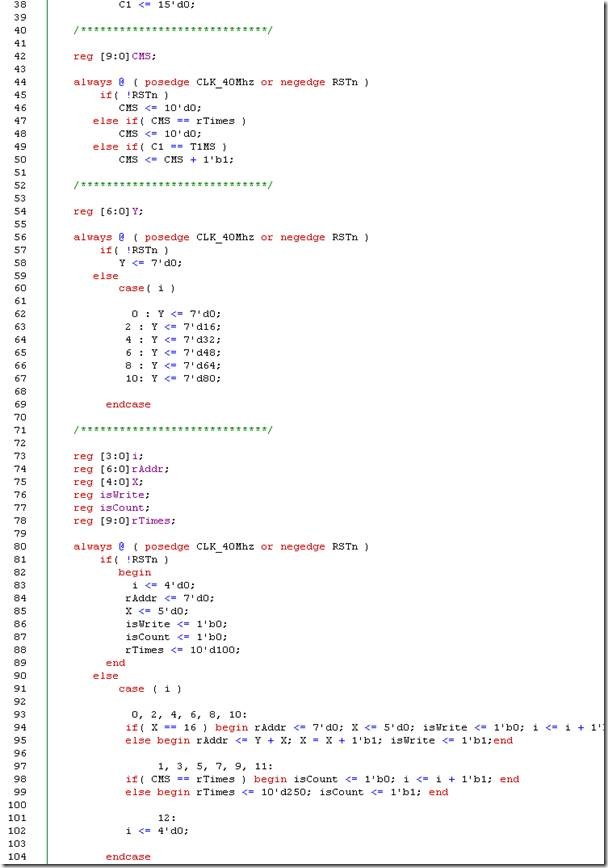

sync_module.v

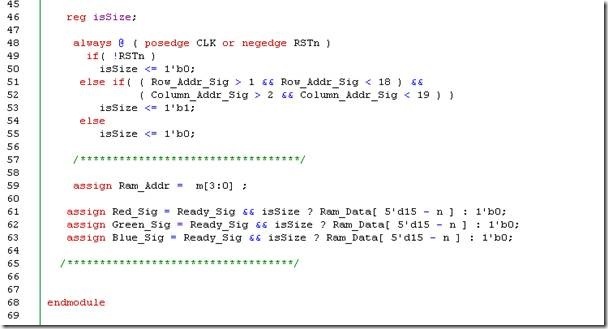

在29行的if条件,就是表示开始显示位置 Y, 和39行的开始显示位置 X。

我们知道图像信息是16 x 16。所以,29行的if条件成立范围是在 Row_Addr_Sig > 1 ~ Row_Addr_Sig < 17。同样的在39行的if条件成立范围在 Column_Addr_Sig > 2 ~ Column_Addr_Sig < 19。

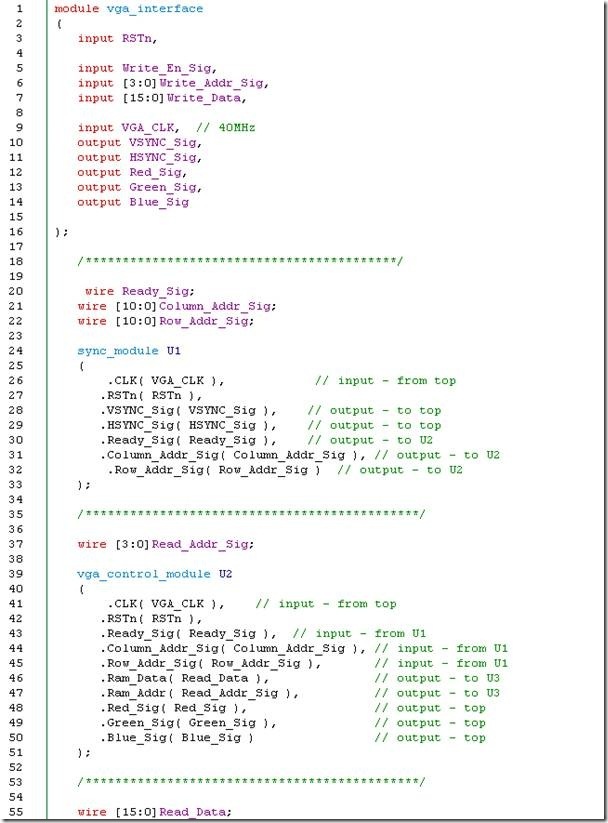

ram_module.v

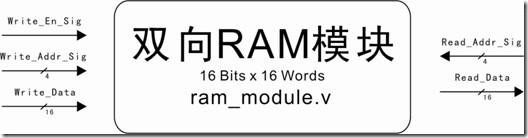

在这里,我们先要考虑 vga_interface.v 支持的图像分辨率,亦即 16 x 16 。所以RAM所需要的储存空间是 16Bits x 16 Words。RAM和 FIFO一样,要访问RAM的时候都需要拉高 xx_En_Sig 信号。由于RAM 包含 16 Bits 所以 Write_Data 和 Read_Data, 皆是16位的位宽。当然,16 Words 表示了 xx_Addr_Sig 是 4位的位宽。

第1~11行是RAM模块的输入输出口。在15行,声明了 16Bits x 16 Words 的储存器。

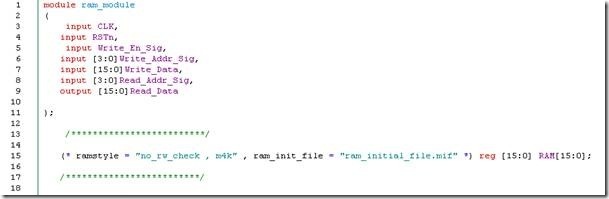

如果以Altera的FPGA为例,尝试回想一下,FPGA都内置了偏上资源 m4k。当我声明储存器的时候,我们可以指定它由 m4k 组成。

(* ram_tyle = m4k *)

当然你也可以指定储存器由逻辑资源组成:

(* ram_tyle = logic *)

在前面,我已经说过:“双向端口的RAM存在访问冲突的问题”。当QuartusII 在综合的时候,由于 m4k 资源本身的特性,并不适合“写时读”(read-during-write),亦即“访问冲突”。虽然,我们手动为RAM模块添加了访问优先级,可以避免“访问冲突”的问题。但是Quartus II 的综合器是一个大笨蛋,你没有提示它:“不用关心m4k资源的访问冲突问题”,综合器是不知道的。因此:

(* ram_style = no_rw_check *)

还有一点就是关于储存器初始化的问题:

还记得在建立ROM的时候,笔者都为ROM建立一个 .mif ,然后对ROM初始化。同样的道理,RAM储存器在创建的时候也必须初始化。该RAM模块初始化的信息,是实验十之五之中的“第一副小绿人”。

(* ram_init_file = ram_initial_file.mif *)

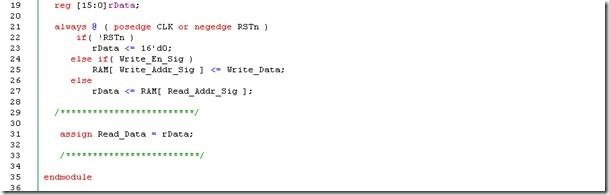

21~27行是RAM模块的访问优先级逻辑。在24行表示了写操作比读操作拥有更高的优先级。当 Write_En_Sig 拉高的时候,对RAM储存器执行写操作。一旦 Write_En_Sig 被拉低 读操作作为RAM储存器的默认状态。

有一重点必须注意就是rData寄存器是用来暂存读数据。为了避免“当写操作执行时Read_Data 失去驱动源”。

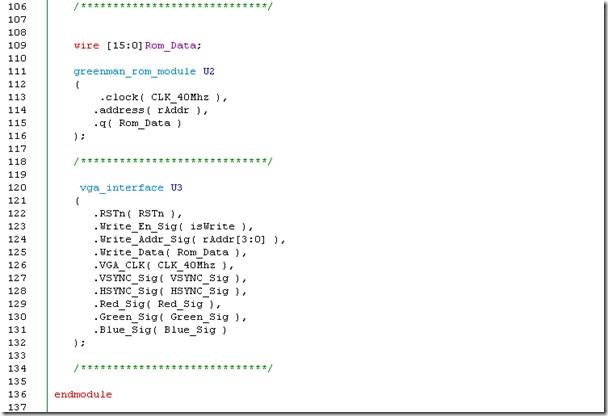

vga_interface.v

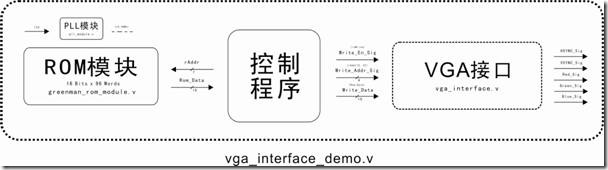

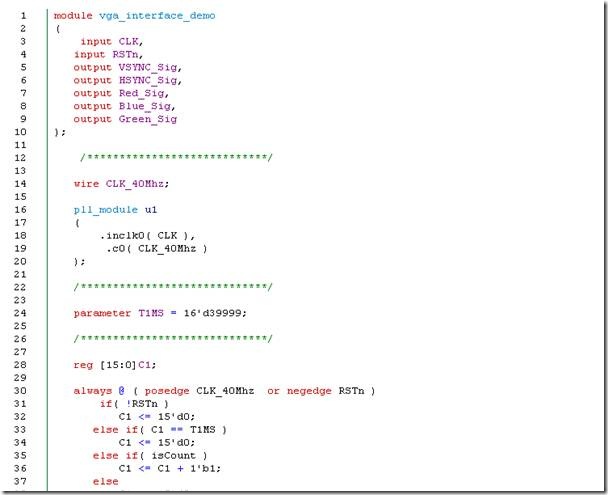

实验十九说明:

读者是不是觉得实验十九和实验九相比,简直是莫名其妙对吧?在这里笔者稍微区分一下实验九和实验十九的不同。实验九顾名思义就是VGA显示模块,它所使用的显示方法是同步的。换句话说,也就是图片信息处理和VGA显示驱动都是在同样的时间下。当然也可以这样想,图片信息是又VGA模块本身提供的,又或者图片信息早已固定存在。

事实上,由于访问优先级逻辑的关系,当发生“访问冲突”的时候,vga_control_module.v读取的是 上一次的rData信息。

实验十九结论:

实验九和实验十九最大的差别就是图像信息处理的方法。前者是由模块内部提供的,后者是由上一层模块写入。此外实验十九当 vga_control_module.v 对 ram_module.v 读取信息的时候,如果在同一个时间,上一层模块对 vga_interface.v 的 ram_module.v 执行写操作,故会发生“访问冲突”。为了避免这个问题,笔者对 ram_module.v 加入了访问优先级逻辑,访问优先级定义为:写操作优先级高于读操作。

实验十九演示:小绿人请加油

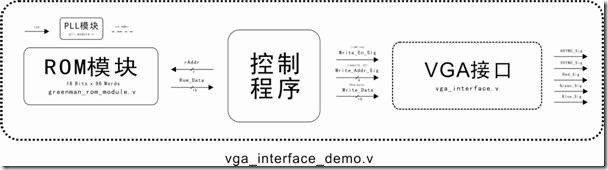

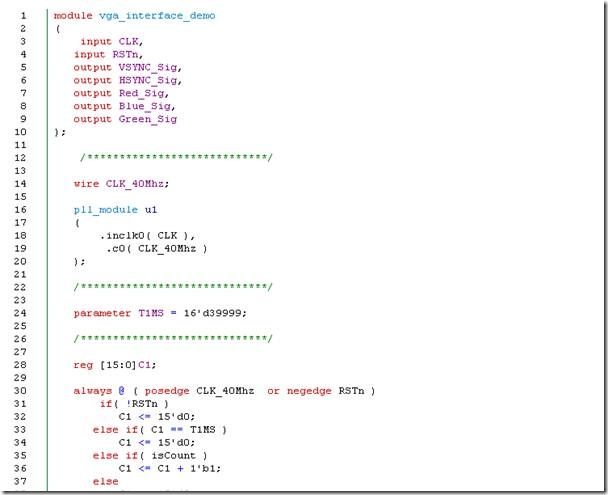

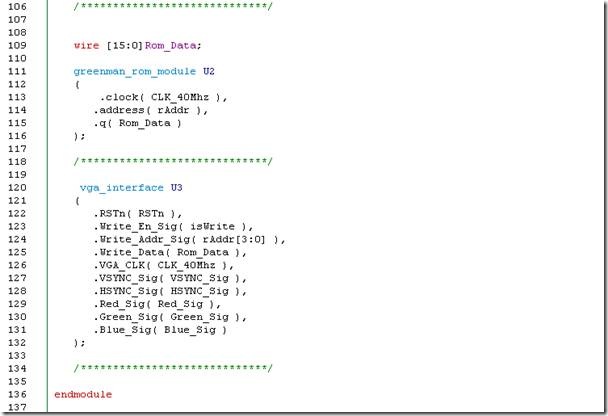

vga_interface_demo.v