从2005年开始,TI相继推出了C645x系列高性能定点DSP,C645x系列DSP 建立在最新的增强型C64x+ DSP内核架构基础之上,基于第三代超长指令结构VelociTI.3。C645x系列DSP主要针对各种基础局端设备应用,包括高端电信设备、无线基础局端以及视频与影像应用等领域。C645x系列DSP不仅为开发人员提供了两倍于 TMS320C641x DSP 的存储器容量与 I/O 带宽,还具备其它高级特性与功能,实现了以低成本满足新一代系统对更高处理性能与更大存储器容量的需求。

C645x系列DSP的主要特点与优势:

◆ 存储器容量与 I/O 带宽是 C641x 的两倍,主频高达1.2G, 峰值运算速度达9600 MMACS(MIPS),而价格与TMS320C6415 DSP 基本相当。

◆ 增强型 C64x+ DSP 内核使系统性能提高了20%,代码长度缩短了20%~30%,同时与 TMS320C64x DSP 实现了 100% 的代码兼容性。

◆ 存储器扩展接口增加支持高性能、大容量的DDR2 SDRAM。

◆ Serial RapidIO (SRIO) 与千兆以太网 MAC 串行器/解串器 (SERDES) 接口支持高效互连通信,可实现高效的处理器间通信。

◆ 新增49条指令。以乘法单元为例,该单元的改善及新增指令加大了乘法运算带宽,支持32位乘法和复数乘法,使每周期16×16的MAC数达8个,大大提升了DSP在处理DCT和FFT变换方面的性能。

◆ 新增软件流水缓存(SPLOOP Buffer)。对原C64x内核(C62x和C641x使用的)的软件流水(Software Pipeline)进一步提升DSP的处理性能,它既可以战胜多周期指令延时对CPU处理性能的影响,还可以在流水线运行阶段的每个周期输出一个或多个处理结果。

◆ 支持紧凑指令(Compact Instructions)。原C64x 内核只支持定长取指包,而C64x+内核支持带“头”的取指包,指令包头标注了该指令包中其它7个字中,哪些是32位的操作码,哪些是16位的操作码。支持紧凑指令可以节省程序存储空间;也能增添程序Cache的命中率。

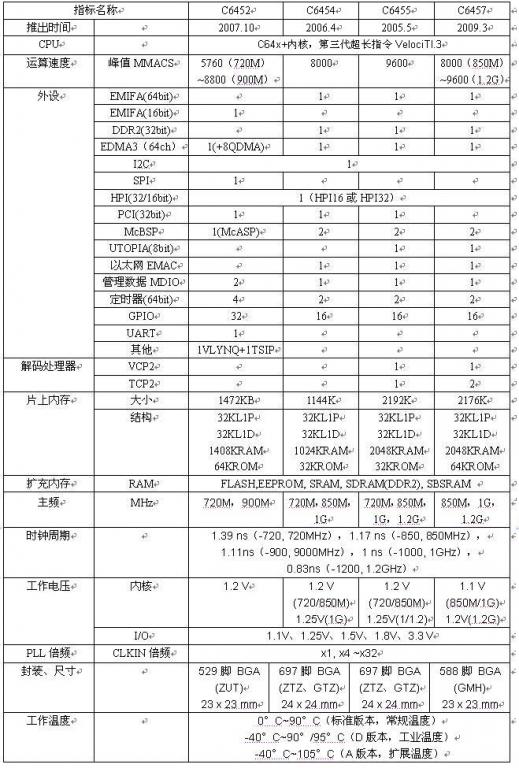

C645x性能指标一览表(见附件)