引 言

随着社会信息交流需求的急剧增加、个人移动通信的迅速普及,频谱已成为越来越宝贵的资源。天线技术采用空分复用(SDMA),利用在信号传播方向上的差别,将同频率、同时隙的信号区分开来。它可以成倍地扩展通信容量,并和其他复用技术相结合,最大限度地利用有限的频谱资源。另外在移动通信中,由于复杂的地形、建筑物结构对电波传播的影响,大量用户间的相互影响,产生时延扩散、瑞利衰落、多径、共信道干扰等,使通信质量受到严重影响。采用智能天线可以有效的解决这个问题。

目前迫切需要解决的是语音、视频和数据三重播放的应用问题。三重播放的核心集中在连接性和计算能力上。连接性就是必须实现不同设备、板卡和系统之间数据的高速通信;计算能力指设备、板卡和系统中的处理器能够满足新的复杂的算法要求。数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。德州仪器、Freescale等半导体厂商在这一领域拥有很强的实力。

1 串行RapidIO及其结构

RapidIO互连技术在2001年完成基本规范。2003年10月,国际标准组织和国际电工委员会(IEC)一致通过了RapidIO互连规范,即ISO/IEC DIS 18372。目前在系统逻辑器件、FPGA和ASIC器件中已经实现了该技术。TI公司经过努力,也已经在DSP芯片上实现了该项技术。串行RapidIO互连架构解决了高性能嵌入式系统在可靠性和互连性方面的挑战。嵌入式系统是“控制、监视或者辅助装置、机器和设备运行的装置”(devices used to control, monitor, or assist

the operation of equipment, machinery or plants)。从中可以看出嵌入式系统是软件和硬件的综合体,还可以涵盖机械等附属装置。目前国内一个普遍被认同的定义是:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

基于DSP的串行RapidIO的主要特点有:

①引脚数少;

②数据宽度和速度可调;

③具备DMA和消息传递功能;

④支持复杂可调整的拓扑结构;

⑤支持多点传送;

⑥可靠性高,可提供服务质量保证;

⑦功耗低。

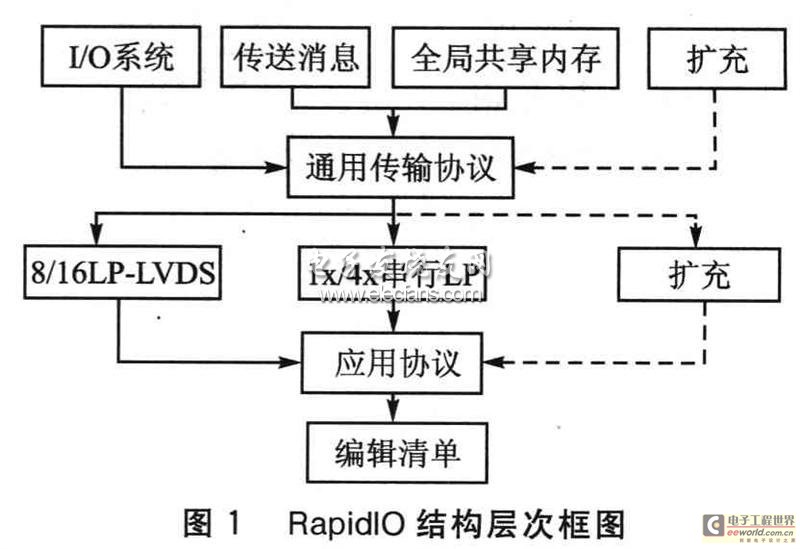

C645x的串行RapidIO有3层结构,如图1所示。RapidIO结构主要包括物理层、传输层和逻辑层。其中物理层负责描述器件的接口规范,例如分组传输机制、流量控制、电特性以及低级错误管理等;传输层为在不同端点设备之间传送分组提供路由信息,交换设备以基于器件的路由方式工作于传输层;逻辑层定义总体的协议和分组格式,每个分组最多包含256字节的载荷,事务通过Load、Store或DMA操作来访问地址空间。图1中,逻辑层包括I/0系统、传送消息、全局共享内存以及为将来可能增加功能预留的扩充单元。

2 系统硬件结构

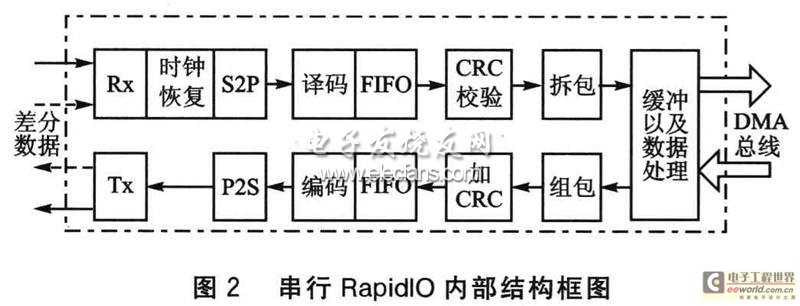

TMS320C645x系列DSP为TI公司推出的速度达到1.2 GHz的DSP,主要应用于电信、医疗电子和新兴的电子行业;可以连接32位DDR2内存和66 MHz的PCI接口;具有2个串行干兆媒体独立接口、以太网MAC端口、1个千兆以太网关,还有一个用于无缝连接公共电信数据流的电信串行接口。TMS320C645x具有的这些特性非常适合于超高速数据处理系统中。在高速数据系统中,大量数据的芯片之间的传输十分关键。只有快速、及时地将数据传输出去或者读取进来,才可以减轻系统对数据存储的压力。图2为TMS320C645x系列DSP的串行Ra—pidIO内部结构框图。

从图2可以看出,接收到的差分数据进入串行Ra—pidI0,首先RapidIO模块根据数据的上升沿变化速度检测出数据发送时钟频率,并以此频率来接收后面的数据。然后,将接收的串行数据经过S2P(Series to Parallel)单元,将串行数据转换成10位的并行数据,从而降低了10倍数据传输速度。物理层得到并行数据后,将数据送到逻辑层,依次经过译码、FIFO、CRC校验和拆包处理,送到缓冲并进行数据处理,最后经过DMA总线送到DSP处理单元,完成数据的接收。

2个DSP之间的RapidIO连接简单、方便,如图3所示,只要将收发数据相应地连接上就可以了。由于RapidIO有4根并行数据总线,如果将所有的数据总线全部连接上,可以确保最高的通信速率。也可以使用1根数据总线通信,这时数据传输速度降低到最高通信速率的1/4。如果多个DSP相互之间都需要进行通信,则一般采用单根数据通信方式。图4中的3个DSP之间相互使用RapidIO总线通信。此外,DSP之间的数据地和模拟地需要分别连接在一起(见图3)。

RapidIO总线的设置有3个步骤:

①设置RapidIO的时钟,通过SERDES_CFG_CNTL寄存器设置数据收发的速率;

②使能RapidIO的接收器,同时设置一些和数据接收相关的参数,包括差分信号的自适应均衡设计、相位偏差设置、信号损耗设置等;

③使能RapidIO的发送器,同时设置一些和数据发送相关的参数,包括发送速率、总线宽度等。

设置RapidIO速率为3.125 Gbps,使能接收器和发送器的代码如下:

开始和结束都是由主机发起和控制的,从机被动地接收命令并执行指令。当从机需要主动向主机发送数据时,只能由从机发出中断到主机;主机响应中断后,发出数据读取命令。具体的工作流程如图5所示。主机的命令发起机构发出操作命令,并将发送请求包经过命令传输机构传送到从机的命令执行机构,从机的命令执行机构可能执行数据接收(主机向从机发送数据)和数据发送(主机要求从机发送数据)任务。命令执行机构处理完成相应命令,发送应答包到主机,主机判断到命令完成,将命令状态清除,完成整个命令的操作。

RapidIO在数据传输过程中,可能产生错误。根据错误情况,RapidIO发出2种不同的中断到CPU:状态错误,此时CPU应复位或者重新同步RapidIO;严重错误,此时CPU应复位所有和RapidIO相关的设备。

4 总 结

本文介绍了DSP中的串行RapidIO总线,详述了该总线的层次结构和内部结构,并且结合多个DSP之间的RapidIO通信介绍了硬件和软件系统设计。该总线可以实现10 Gbps的高速数据通信,可以满足语音、图像和数据等多种通信业务的需求。整个通信系统连接简单、通信可靠、实用性强

(本文转自电子工程世界:http://eeworld.com/gykz/2011/0921/article_8560.html)