在计算机领域,通常用Endian和Endianness指出在计算机的存储器中字节是怎样组织的。

Endian有如下的三种模式:

(1)Big Endian

(2)Little Endian

(3)Mixed(Middle) Endian

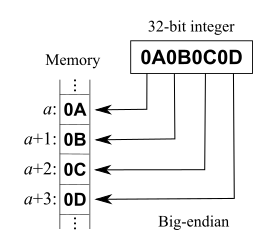

Examples of storing the value 0A0B0C0Dh in memory

Note that hexadecimal notation is used.

To illustrate the notions this section provides example layouts of the 32-bit number 0A0B0C0Dh in the most common variants of endianness. There exist

several digital processors that use other formats, but these two are the most common in general processors. That is true for typical embedded

systems as well as for general computer CPU(s). Most processors used in non CPU roles in typical computers (in storage units, peripherals etc.) also use one of these two basic formats, although not always 32-bit of course.

All the examples refer to the storage in memory of the value.

Big-endian

Atomic element size 8-bit, address increment 1-byte (octet)

| increasing addresses → | |||||

| 0Ah | 0Bh | 0Ch | 0Dh | ||

The most significant byte (MSB)

value, which is 0Ah in our example, is stored at the memory location with the lowest address, the next byte value in significance,0Bh,

is stored at the following memory location and so on. This is akin to Left-to-Right reading in hexadecimal order.

Atomic element size 16-bit

| increasing addresses → | |||||

| 0A0Bh | 0C0Dh | ||||

The most significant atomic element stores now the value 0A0Bh, followed by 0C0Dh.

Little-endian

Atomic element size 8-bit, address increment 1-byte (octet)

| increasing addresses → | |||||

| 0Dh | 0Ch | 0Bh | 0Ah | ||

The least significant byte (LSB)

value, 0Dh, is at the lowest address. The other bytes follow in increasing order of significance.

Atomic element size 16-bit

| increasing addresses → | |||||

| 0C0Dh | 0A0Bh | ||||

The least significant 16-bit unit stores the value 0C0Dh, immediately followed by 0A0Bh.

Note that 0C0Dh and 0A0Bh represent integers,

not bit layouts (see bit numbering).

Byte addresses increasing from right to left

Visualising memory addresses from left to right makes little-endian values appear backwards. If the addresses are written increasing towards the left instead, each individual little-endian value will appear forwards. However

strings of values or characters appear reversed instead.

With 8-bit atomic elements:

| ← increasing addresses | |||||

| 0Ah | 0Bh | 0Ch | 0Dh | ||

The least significant byte (LSB)

value, 0Dh, is at the lowest address. The other bytes follow in increasing order of significance.

With 16-bit atomic elements:

| ← increasing addresses | |||||

| 0A0Bh | 0C0Dh | ||||

The least significant 16-bit unit stores the value 0C0Dh, immediately followed by 0A0Bh.

The display of text is reversed from the normal display of languages such as English that read from left to right. For example, the word "XRAY" displayed in this manner, with each character stored in an 8-bit atomic element:

| ← increasing addresses | |||||

| "Y" | "A" | "R" | "X" | ||

If pairs of characters are stored in 16-bit atomic elements (using 8 bits per character), it could look even stranger:

| ← increasing addresses | |||

| "AY" | "XR" | ||

This conflict between the memory arrangements of binary data and text is intrinsic to the nature of the little-endian convention, but is a conflict only for languages written left-to-right, such as English. For right-to-left languages such as Arabic and Hebrew,

there is no conflict of text with binary, and the preferred display in both cases would be with addresses increasing to the left. (On the other hand, right-to-left languages have a complementary intrinsic conflict in the big-endian system.)

Middle-endian

Numerous other orderings, generically called middle-endian or mixed-endian, are possible. On the PDP-11 (16-bit

little-endian) for example, the compiler stored 32-bit values with the 16-bit halves swapped from the expected little-endian order. This ordering is known as PDP-endian.

- storage of a 32-bit word on a PDP-11

| increasing addresses → | |||||

| 0Bh | 0Ah | 0Dh | 0Ch | ||

The ARM architecture can also produce this format when writing

a 32-bit word to an address 2 bytes from a 32-bit word alignment

Segment descriptors on Intel

80386 and compatible processors keep a base 32-bit address of the segment stored in little-endian order, but in four nonconsecutive bytes, at relative positions 2,3,4 and 7 of the descriptor start.