转用MDK有一段时间了,越来越觉得MDK的强大,因为我之前都是用ADS1.2开发产品,所以更能体会到MDK的强大与易用性。MDK编译出来的代码与ADS1.2相比,代码量减少了很多,我的一个工程用ADS1.2编译为25.4KB(都是bin格式),但用MDK编译出来仅有19.5KB(采用默认优化级别,即L2优化级别)。根据我个人的经验,使用一个新的编译器,难点往往有三个,一个是建立一个新的工程,以及工程项目的配置;二是启动代码的编写;三是如何下载和单步调试。今天重点写一下MDK的启动代码。使用MDK版本为V4.01。

MDK编译器所追求的是要让arm 处理器像单片机那样简单使用,所以每个厂家的各种ARM,MDK都会有一个自带的启动代码,值得提出的是,这个启动代码可以用图形化界面来配置,这对刚入门的人来说绝对是一条捷径。

下面看一下MDK的启动代码以及图形化界面。

1.新建一个工程

单击Project ->New...->µVision Project菜单项,µVision 4将打开一个标准对话框,输入希望新建工程的名字即可创建一个新的工程,建议对每个新建工程使用独立的文件夹。

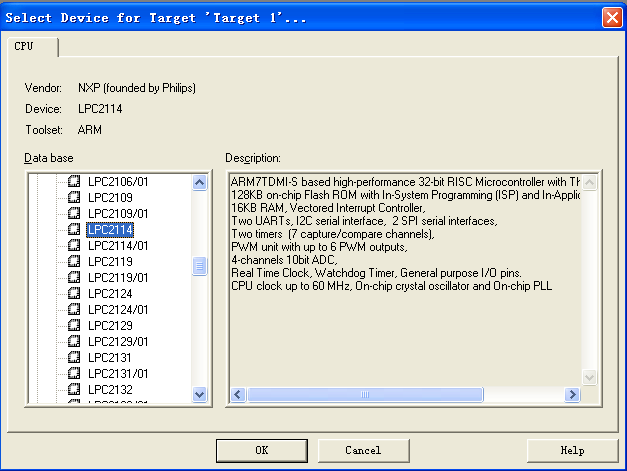

2.选择设备

在创建一个新的工程时,µVision要求为这个工程选择一款CPU。选择设备对话框显示了µVision的设备数据库,只需要选择用户所需的微控制器即可。例如,选择 Philips LPC2114微控制器,这个选择设置了LPC2114设备的必要工具选项、简化了工具的配置。

当创建一个新的工程时,µVision会自动为所选择的CPU添加合适的启动代码。如下图,点击确定即可复制LPC2100的启动代码。

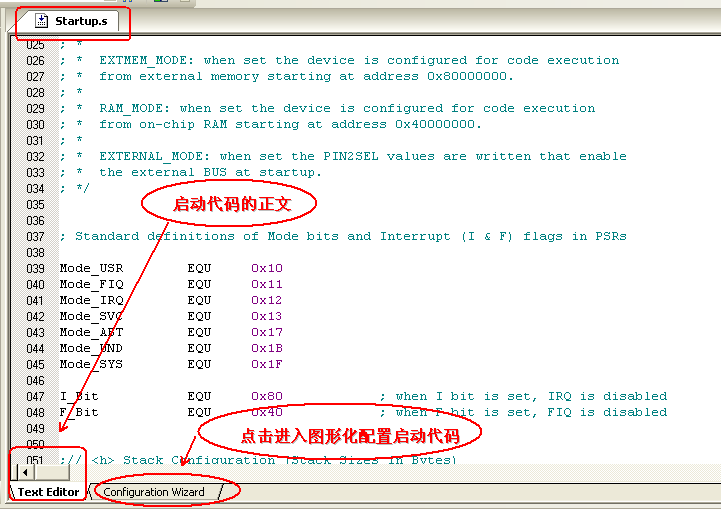

启动代码的正文如下所示:

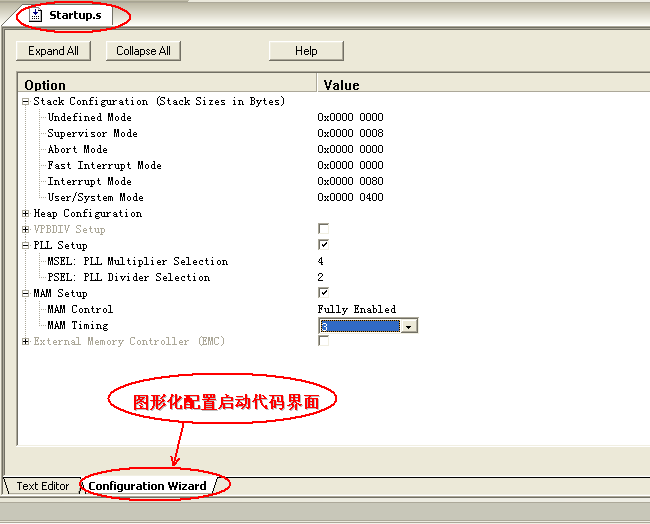

启动代码的图形配置界面:

µVision 4的配置向导通过菜单的方式对汇编程序、C程序或调试初始化文件进行配置。在配置文件中,对应这些配置菜单的是控制项(和html中的标签相似),它们嵌入在配置文件的注释中。

下面对启动代码做详细注释:

;/*****************************************************************************/

;/* STARTUP.S: Startup file for Philips LPC2000 */

;/*****************************************************************************/

;/* <<< Use Configuration Wizard in Context Menu >>> */

;/*****************************************************************************/

;/* This file is part of the uVision/ARM development tools. */

;/* Copyright (c) 2005-2007 Keil Software. All rights reserved. */

;/* This software may only be used under the terms of a valid, current, */

;/* end user licence from KEIL for a compatible version of KEIL software */

;/* development tools. Nothing else gives you the right to use this software. */

;/*****************************************************************************/

这段是一些说明,无非说些版权,时间信息等,注意红色标注出的语句必须在前100行文本中声明如下语句,这样编辑器将以配置向导视图的形式打开配置文件。

; Standard definitions of Mode bits and Interrupt (I & F) flags in PSRs

Mode_USR EQU 0x10

Mode_FIQ EQU 0x11

Mode_IRQ EQU 0x12

Mode_SVC EQU 0x13

Mode_ABT EQU 0x17

Mode_UND EQU 0x1B

Mode_SYS EQU 0x1F

I_Bit EQU 0x80 ; when I bit is set, IRQ is disabled

F_Bit EQU 0x40 ; when F bit is set, FIQ is disabled

这段代码用于定义一些模式,以及定义中断屏蔽位。

;// <h> Stack Configuration (Stack Sizes in Bytes)

;// <o0> Undefined Mode <0x0-0xFFFFFFFF:8>

;// <o1> Supervisor Mode <0x0-0xFFFFFFFF:8>

;// <o2> Abort Mode <0x0-0xFFFFFFFF:8>

;// <o3> Fast Interrupt Mode <0x0-0xFFFFFFFF:8>

;// <o4> Interrupt Mode <0x0-0xFFFFFFFF:8>

;// <o5> User/System Mode <0x0-0xFFFFFFFF:8>

;// </h>

UND_Stack_Size EQU 0x00000000

SVC_Stack_Size EQU 0x00000008

ABT_Stack_Size EQU 0x00000000

FIQ_Stack_Size EQU 0x00000000

IRQ_Stack_Size EQU 0x00000080

USR_Stack_Size EQU 0x00000400

ISR_Stack_Size EQU (UND_Stack_Size + SVC_Stack_Size + ABT_Stack_Size + /

FIQ_Stack_Size + IRQ_Stack_Size)

AREA STACK, NOINIT, READWRITE, ALIGN=3

Stack_Mem SPACE USR_Stack_Size

__initial_sp SPACE ISR_Stack_Size

Stack_Top

这一段配置堆栈空间,注意红色部分可以生成图形化的界面,

<h>--Heading标题:表示以下选项在一个组中,直到遇到</h> ,表示Heading标题标题结束。

<ox>(x=1,2,3...)--表示可以指定一个值的范围

User/System Mode <0x0-0xFFFFFFFF:8>--表示用户模式下堆栈范围为0~0xFFFFFFFF之间,数字“8”表示每次递增或递减的步长为8.

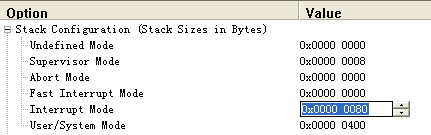

上面代码生成的图形化配置界面如下图:

若将上图的interrupt Mode的值该为0x0000 0100,则启动代码的“IRQ_Stack_Size EQU 0x00000080”自动变为“IRQ_Stack_Size EQU 0x00000100”

;// <h> Heap Configuration

;// <o> Heap Size (in Bytes) <0x0-0xFFFFFFFF>

;// </h>

Heap_Size EQU 0x00000000

AREA HEAP, NOINIT, READWRITE, ALIGN=3

__heap_base

Heap_Mem SPACE Heap_Size

__heap_limit

配置堆的大小,情况与配置堆栈十分相识。

;// <e> VPBDIV Setup

;// <i> Peripheral Bus Clock Rate

;// <o1.0..1> VPBDIV: VPB Clock

;// <0=> VPB Clock = CPU Clock / 4

;// <1=> VPB Clock = CPU Clock

;// <2=> VPB Clock = CPU Clock / 2

;// <o1.4..5> XCLKDIV: XCLK Pin

;// <0=> XCLK Pin = CPU Clock / 4

;// <1=> XCLK Pin = CPU Clock

;// <2=> XCLK Pin = CPU Clock / 2

;// </e>

VPBDIV_SETUP EQU 1

VPBDIV_Val EQU 0x00000000

; Phase Locked Loop (PLL) definitions

PLL_BASE EQU 0xE01FC080 ; PLL Base Address

PLLCON_OFS EQU 0x00 ; PLL Control Offset

PLLCFG_OFS EQU 0x04 ; PLL Configuration Offset

PLLSTAT_OFS EQU 0x08 ; PLL Status Offset

PLLFEED_OFS EQU 0x0C ; PLL Feed Offset

PLLCON_PLLE EQU (1<<0) ; PLL Enable

PLLCON_PLLC EQU (1<<1) ; PLL Connect

PLLCFG_MSEL EQU (0x1F<<0) ; PLL Multiplier

PLLCFG_PSEL EQU (0x03<<5) ; PLL Divider

PLLSTAT_PLOCK EQU (1<<10) ; PLL Lock Status

配置VPBDIV

<e> --Heading且Enable标题:表示以下选项在一个组中,选项可通过Checkbox使能

<o1.0..1>---修改数值的指定位

上面代码生成的图形化配置界面如下图:

;// <e> PLL Setup

;// <o1.0..4> MSEL: PLL Multiplier Selection

;// <1-32><#-1>

;// <i> M Value

;// <o1.5..6> PSEL: PLL Divider Selection

;// <0=> 1 <1=> 2 <2=> 4 <3=> 8

;// <i> P Value

;// </e>

PLL_SETUP EQU 1

PLLCFG_Val EQU 0x00000023

配置PLL。情况与配置VPBDIV十分相似。

; Memory Accelerator Module (MAM) definitions

MAM_BASE EQU 0xE01FC000 ; MAM Base Address

MAMCR_OFS EQU 0x00 ; MAM Control Offset

MAMTIM_OFS EQU 0x04 ; MAM Timing Offset

;// <e> MAM Setup

;// <o1.0..1> MAM Control

;// <0=> Disabled

;// <1=> Partially Enabled

;// <2=> Fully Enabled

;// <i> Mode

;// <o2.0..2> MAM Timing

;// <0=> Reserved <1=> 1 <2=> 2 <3=> 3

;// <4=> 4 <5=> 5 <6=> 6 <7=> 7

;// <i> Fetch Cycles

;// </e>

MAM_SETUP EQU 1

MAMCR_Val EQU 0x00000002

MAMTIM_Val EQU 0x00000004

配置存储器加速模块,情况与配置VPBDIV十分相似。

; External Memory Controller (EMC) definitions

EMC_BASE EQU 0xFFE00000 ; EMC Base Address

BCFG0_OFS EQU 0x00 ; BCFG0 Offset

BCFG1_OFS EQU 0x04 ; BCFG1 Offset

BCFG2_OFS EQU 0x08 ; BCFG2 Offset

BCFG3_OFS EQU 0x0C ; BCFG3 Offset

;// <e> External Memory Controller (EMC)

EMC_SETUP EQU 0

;// <e> Bank Configuration 0 (BCFG0)

;// <o1.0..3> IDCY: Idle Cycles <0-15>

;// <o1.5..9> WST1: Wait States 1 <0-31>

;// <o1.11..15> WST2: Wait States 2 <0-31>

;// <o1.10> RBLE: Read Byte Lane Enable

;// <o1.26> WP: Write Protect

;// <o1.27> BM: Burst ROM

;// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

;// <2=> 32-bit <3=> Reserved

;// </e>

BCFG0_SETUP EQU 0

BCFG0_Val EQU 0x0000FBEF

;// <e> Bank Configuration 1 (BCFG1)

;// <o1.0..3> IDCY: Idle Cycles <0-15>

;// <o1.5..9> WST1: Wait States 1 <0-31>

;// <o1.11..15> WST2: Wait States 2 <0-31>

;// <o1.10> RBLE: Read Byte Lane Enable

;// <o1.26> WP: Write Protect

;// <o1.27> BM: Burst ROM

;// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

;// <2=> 32-bit <3=> Reserved

;// </e>

BCFG1_SETUP EQU 0

BCFG1_Val EQU 0x0000FBEF

;// <e> Bank Configuration 2 (BCFG2)

;// <o1.0..3> IDCY: Idle Cycles <0-15>

;// <o1.5..9> WST1: Wait States 1 <0-31>

;// <o1.11..15> WST2: Wait States 2 <0-31>

;// <o1.10> RBLE: Read Byte Lane Enable

;// <o1.26> WP: Write Protect

;// <o1.27> BM: Burst ROM

;// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

;// <2=> 32-bit <3=> Reserved

;// </e>

BCFG2_SETUP EQU 0

BCFG2_Val EQU 0x0000FBEF

;// <e> Bank Configuration 3 (BCFG3)

;// <o1.0..3> IDCY: Idle Cycles <0-15>

;// <o1.5..9> WST1: Wait States 1 <0-31>

;// <o1.11..15> WST2: Wait States 2 <0-31>

;// <o1.10> RBLE: Read Byte Lane Enable

;// <o1.26> WP: Write Protect

;// <o1.27> BM: Burst ROM

;// <o1.28..29> MW: Memory Width <0=> 8-bit <1=> 16-bit

;// <2=> 32-bit <3=> Reserved

;// </e>

BCFG3_SETUP EQU 0

BCFG3_Val EQU 0x0000FBEF

;// </e> End of EMC

配置外部存储器,情况和配置VPBDIV类似。

; External Memory Pins definitions

PINSEL2 EQU 0xE002C014 ; PINSEL2 Address

PINSEL2_Val EQU 0x0E6149E4 ; CS0..3, OE, WE, BLS0..3,

; D0..31, A2..23, JTAG Pins

定义外部存储器引脚。

PRESERVE8

; Area Definition and Entry Point

; Startup Code must be linked first at Address at which it expects to run.

AREA RESET, CODE, READONLY

ARM ;声明使用ARM模式

默认连接下,启动代码必须放在RESET段内

; Exception Vectors

; Mapped to Address 0.

; Absolute addressing mode must be used.

; Dummy Handlers are implemented as infinite loops which can be modified.

Vectors LDR PC, Reset_Addr ;定义异常向量-复位

LDR PC, Undef_Addr ;未定义指令

LDR PC, SWI_Addr ;软件中中断

LDR PC, PAbt_Addr ;预取指中止

LDR PC, DAbt_Addr ;数据中止

NOP ; Reserved Vector 保留

; LDR PC, IRQ_Addr ;IRQ中断,用下面的语句代替本句,这样能更快的进入中断

LDR PC, [PC, #-0x0FF0] ; 从VicVectAddr寄存器读取中断向量地址. 当CPU执行这条指令还没有跳转时,

; PC的值为0x0000 0020. 0x0000 0020减去0x0ff0为0xFFFF F030这是向量控制寄

; 存器的特殊寄存器VicVectAddr,这个寄存器保存当前IRQ中断服务程序的入口地址

LDR PC, FIQ_Addr

Reset_Addr DCD Reset_Handler ;默认连接下,复位异常服务函数名必须声明为Reset_Handler,这是程序默认入口

Undef_Addr DCD Undef_Handler

SWI_Addr DCD SWI_Handler

PAbt_Addr DCD PAbt_Handler

DAbt_Addr DCD DAbt_Handler

DCD 0 ; Reserved Address

IRQ_Addr DCD IRQ_Handler

FIQ_Addr DCD FIQ_Handler

Undef_Handler B Undef_Handler ;跳转到复位异常服务函数

SWI_Handler B SWI_Handler ;一般情况下,由于PLC2100系列并不需要软件中断,预取指中止等异常,所以这些

PAbt_Handler B PAbt_Handler ;异常服务程序只是原地循环

DAbt_Handler B DAbt_Handler

IRQ_Handler B IRQ_Handler

FIQ_Handler B FIQ_Handler